## On the Electrostatics of Double-Gate and Cylindrical Nanowire MOSFETs

Elena Gnani, Susanna Reggiani, Massimo Rudan and Giorgio Baccarani ARCES and DEIS, University of Bologna, Viale Risorgimento 2, I-40136 Bologna, Italy email: egnani@deis.unibo.it

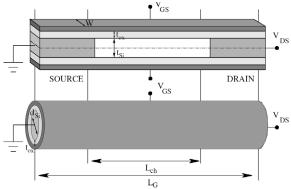

In view of a number of roadblocks which prevent standard MOSFET scaling according to the ITRS provisions, new device architectures are being investigated in order to exploit the ultimate potential of the CMOS technology. Among such architectures, double-gate (DG) MOSFETs have been developed in view of their performance advantages [1], i.e. the containment of the short-channel and DIBL effects. Their control is further improved in the gate-all-around (GAA) MOSFET. However, this device is affected by an inverse narrow-width effect due to the enhanced field at the gate edges [2]. The best tradeoff is achieved using a cylindrical nanowire (CNW) MOSFET [3] as pointed out in [4,5] where classical models have been worked out. The schematic view of a cylindrical nanowire device is shown in Fig. 1 (bottom) compared with a DG MOSFET (top). In order to demonstrate the potential enhancement achievable by the CNW MOSFET, new simulation tools suitable for this kind of analysis have been worked out, able to account for the quantum confinement of the mobile charge in the specific cylindrical domain describing the channel section of the device.

In this work we address the electrostatics of fully-depleted DG and CNW MOSFETs at the miniaturization limit of 25 nm effective channel length. In doing so, we solve a 2D Poisson equation coupled with as many 1D Schrödinger equations as the number of mesh points along the channel, and work out a rigorous perturbative approach to the solution of the Schrödinger equation, based on the expansion of the energy eigenfunctions on the complete set of the unperturbed eigenfunctions. Rather than using the standard textbook formulas of the perturbation theory, however, we solve numerically the resulting eigenvalue problem, and determine the exact expansion coefficients. The approach turns out to be stable, and an order-of-magnitude faster than a fully-numerical solution. Then, the Schrödinger-Poisson problem is coupled with a 1-D drift-diffusion (DD) solver in the longitudinal direction of the device. To this purpose, the potential profile along the symmetry axis of the device is taken as an initial condition for the DD solver, and the resulting quasi-Fermi potential is then used as a reference potential for the Schrödinger equation. The solution of the whole system of equations is obtained by iteration.

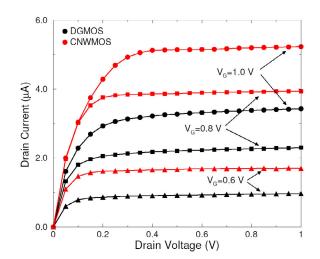

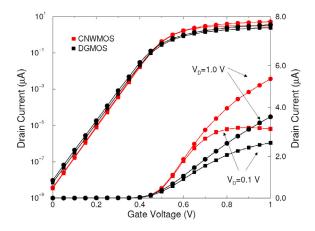

In Fig. 2, the charge distribution and the potential energy within the cross section of both devices are shown at the same bias conditions. Within the cylindrical structure, the total charge is twice as large as that of a DG structure, and electrons distribute farther from the interface leading to an enhanced mobility (see Fig. 3). The output characteristics are computed for both devices and compared in Fig. 3 for an equal cross section. Clearly, the CNW provides higher currents and a smaller output conductance with respect to the DG MOSFET. Also, the available voltage gain  $g_m/g_o$  turns out to be about 37 for the former structure as opposed to 24 for the latter. This makes the CNW MOSFET an interesting device architecture also for analog applications. Finally, the turn-on characteristics are shown in figure 4 and again the CNW exhibits a better performance in terms of subthreshold slope and leakage current, i.e.  $2x10^{-13}$  vs  $10^{-12}$  A/um.

[1] B. Yu et al., IEDM 2002 Tech. Digest, pp. 251-254, 2002.

- [4] C. Auth, J. Plummer, IEEE EDL, vol. 18, pp. 74-76, 1997.

- [5] S.-H. Oh et al., *IEEE EDL*, vol. 21, pp. 445-447, 2000.

A full journal publication of this work will be published in the Journal of Computational Electronics.

<sup>[2]</sup> A. Burenkov et al., ESSDERC 2003 Proceedings, pp. 135-138, 2003.

<sup>[3]</sup> S.-H. Oh et al., IEDM 2000 Tech. Digest, pp. 65-68, 2000.

Fig 1: Structures and reference frame. Top: DG-MOSFET: the silicon thickness  $t_{Si} = 5$  nm, the device width W = 4 nm. Bottom: CNW-MOSFET: the diameter  $d_{Si}$  is 5 nm. Also  $L_G = 50$  nm,  $L_{ch} = 25$  nm,  $t_{ox} = 1$  nm.

Fig 2: Charge distribution and potential energy vs radial coordinate in the cylindrical (a) and linear-box domain (b). The charge distribution is larger and more confined in the cylindrical device for an equal section.

Fig. 3: Output characteristics for the CNW and DG MOSFETS for an equal cross section. The figure shows that the CNW exhibits a smaller output conductance and a larger drain current.

Fig. 4: Turn-on characteristics for the CNW and DG MOSFETS for an equal cross section. The figure shows that the CNW exhibits a slightly larger subthreshold slope and a smaller leakage current at zero bias. The leakage currents turn out to be  $2x10^{-13}$  vs.  $10^{-12}$  A/µm, respectively.

A full journal publication of this work will be published in the Journal of Computational Electronics.