## **TCAD** simulation of statistical variability

Andrew R. Brown

&

The Glasgow Device Modelling Group University of Glasgow

#### Outline

- Introduction

- Sources of variability and TCAD challenges

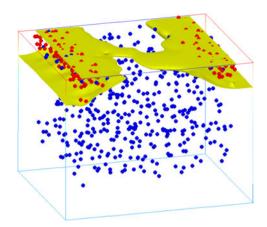

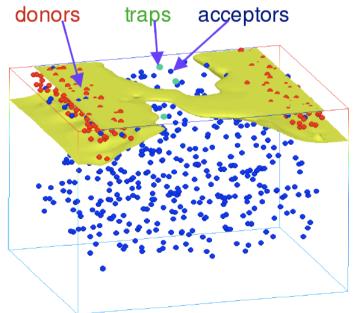

- Random discrete dopants

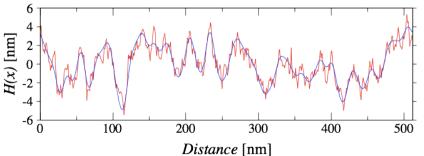

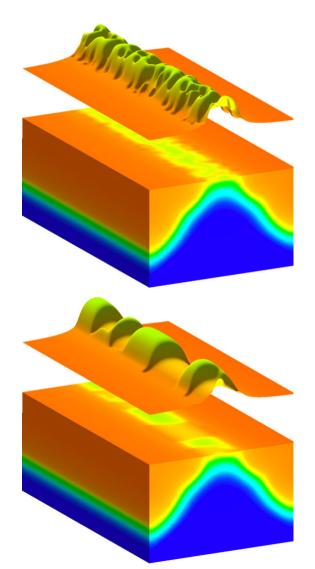

- Line edge roughness

- Poly-silicon gate granularity

- Metal gate granularity

- Statistical Reliability

- Examples

- Conclusion

### Variability Research in Europe

#### Modern

- MOdeling and DEsign of Reliable, process variation-aware Nanoelectronic devices, circuits and systems

- 31 partners in 9 European countries

#### Reality

- Reliable and Variability tolerant System-on-a-chip Design in More-Moore Technologies

- IMEC, STMicroelectronics, ARM, KU Leuven, U. Bologna, U. Glasgow

#### Trams

- Terascale Reliable Adaptive Memory Systems

- UP Catalunya, Intel, IMEC, U. Glasgow

#### Mordred

- Modelling of the reliability and degradation of next generation nanoelectronic devices

- Tampere U. of Tech., UCL, U. Glasgow, Vienna Inst. Micro., IMEC, Infineon, GSS, KU Leuven

#### NanoCMOS (UK)

- Meeting the design challenges of nanoCMOS electronics

- U. Glasgow, U. Manchester, U. Southampton, U. York, U. Edinburgh, NeSC

## Glasgow statistical 3D simulation tools

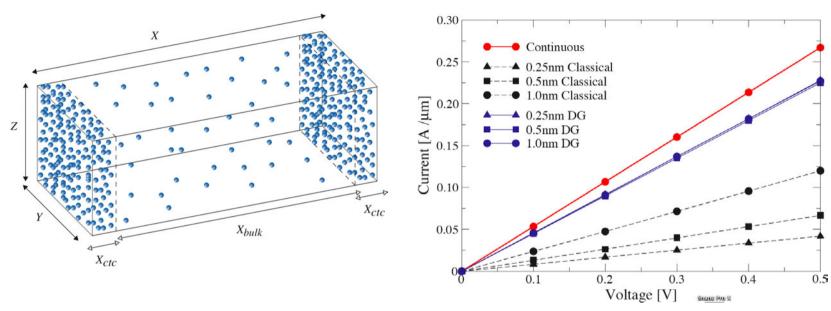

Drift-Diffusion (DD) with quantum corrections.

Ensemble Monte Carlo (MC) with ab-initio impurity scattering.

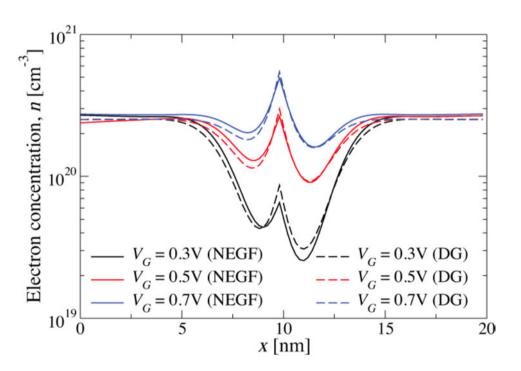

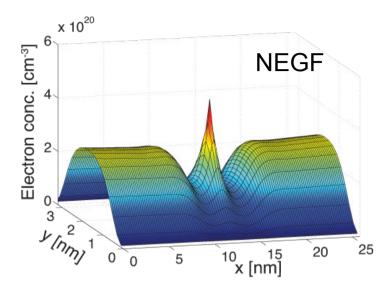

Non-Equilibrium Green's Functions (NEGF).

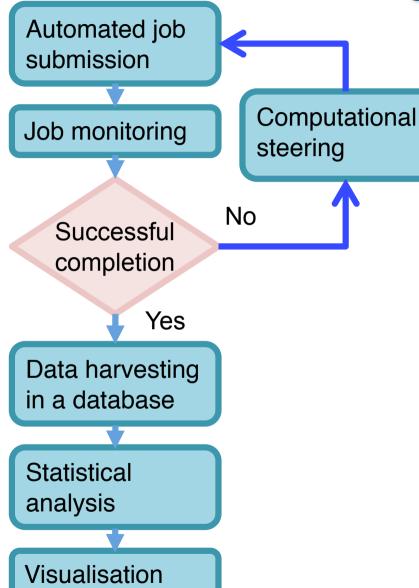

# Grid/cluster based simulation technology

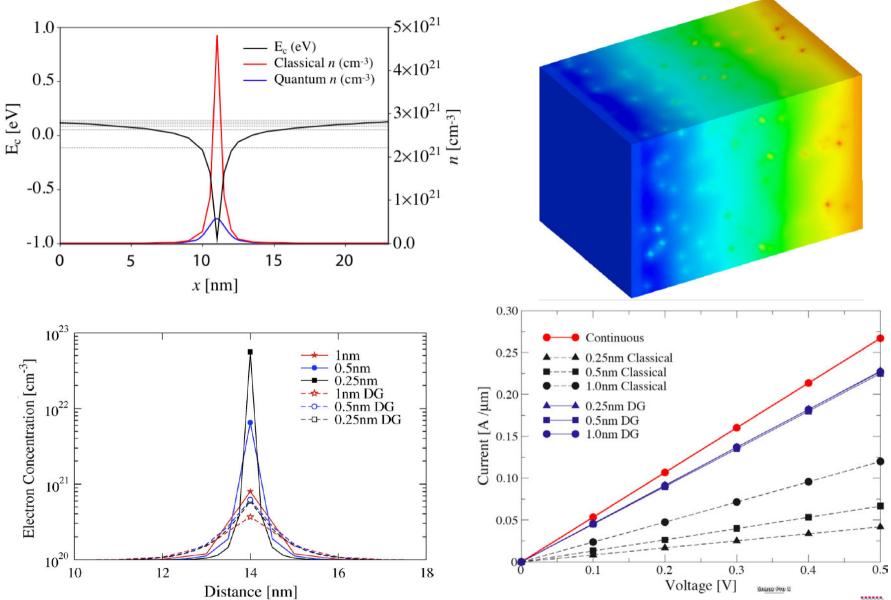

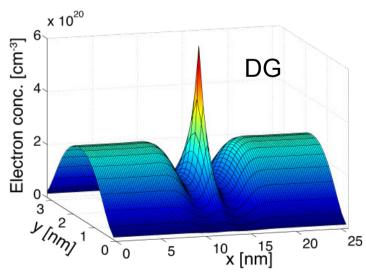

#### Quantum corrections using DG

Simulation and Characterisation of Statistical CMOS Variability and Reliability SISPAD Workshop, Bologna 9/9/2010

#### How accurate is the DG solution?

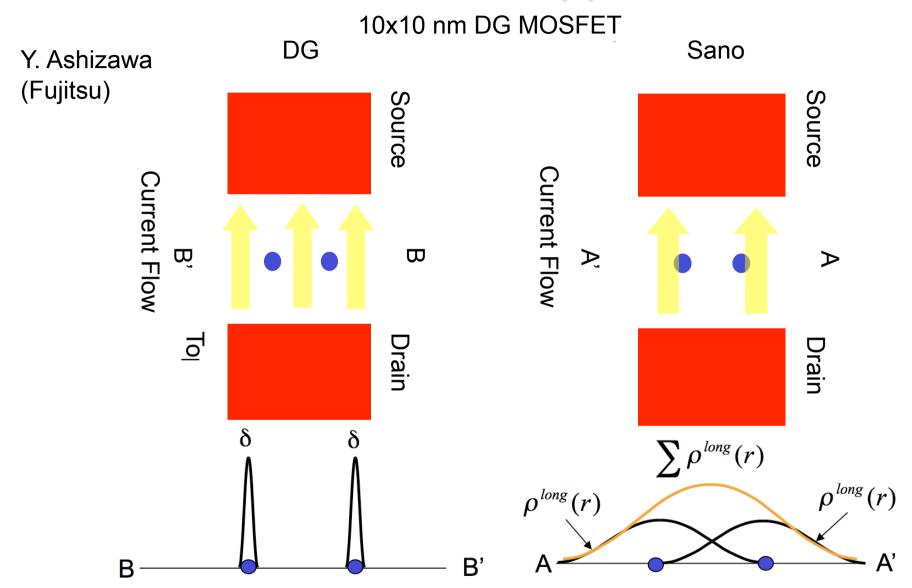

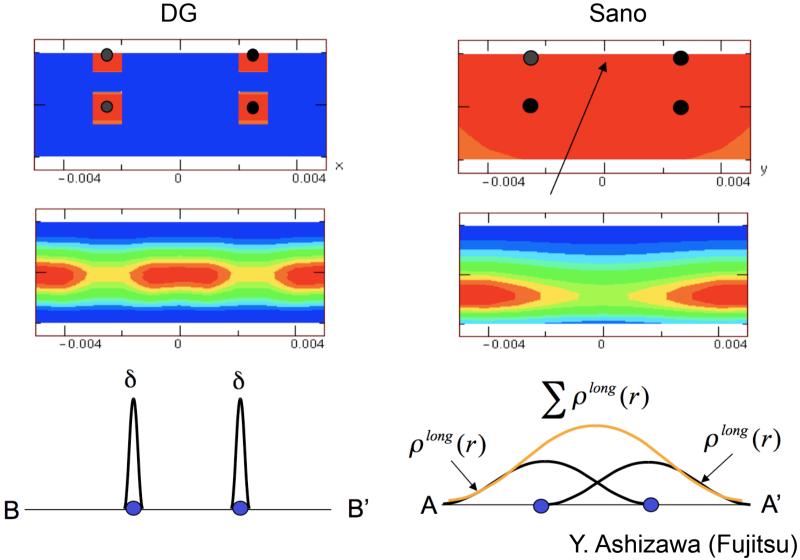

## DG vs. the Sano approach

#### DG vs. the Sano approach

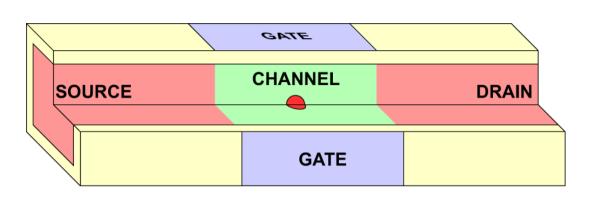

10x10 nm DG MOSFET

# The mobility dilemma (1) Doping concentration dependent mobility

- The mobility is a statistical transport property.

- It has a meaning for sufficiently large self averaging system.

- No mobility can be assigned to individual dopants.

- Best solution is to use the continuous doping from which random dopants were generated.

- Even with DG corrections the resistance of an atomistic slab is larger compared to continuously doped one due to partial localization.

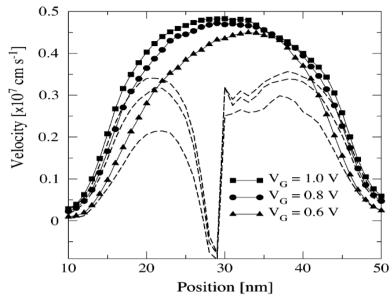

# The mobility dilemma (2) Velocity saturation, field dependence

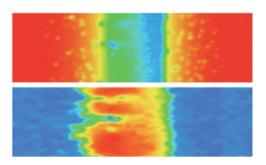

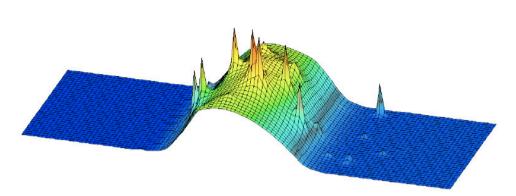

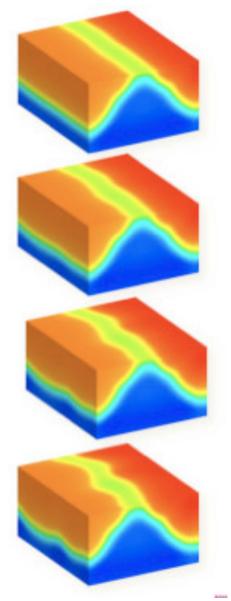

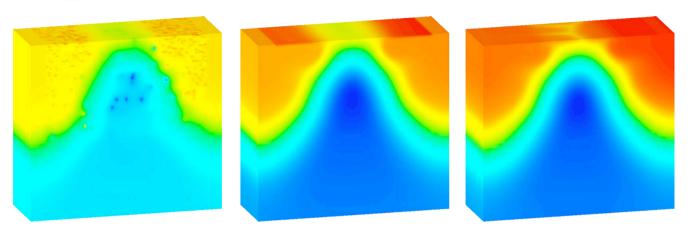

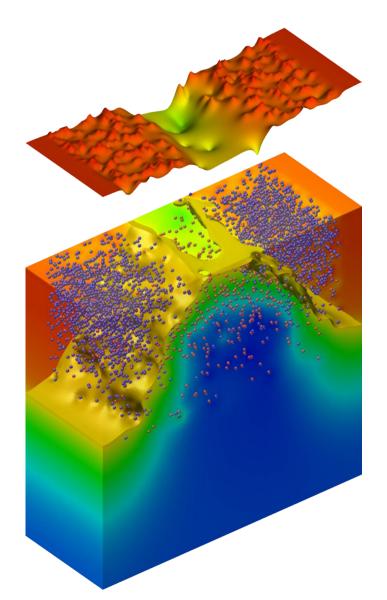

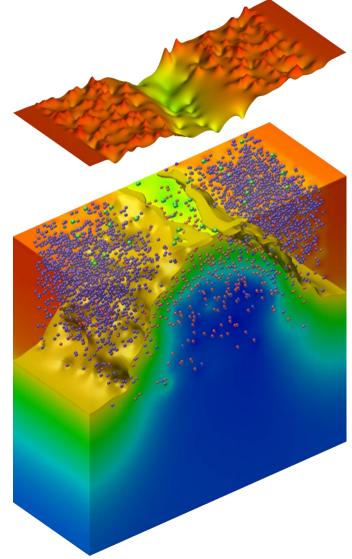

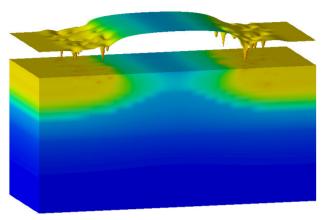

Potential distribution in a MOSFET with random dopants

Velocity distribution in a MOSFET with single dopant

- □ Field dependent mobility has a meaning in 'adiabatic' conditions.

- The high electric field around single dopant cannot be used in the field dependent mobility model.

- The velocity saturation is associated with dissipative phonon scattering.

- The reduction of velocity around single dopant is associated with Coulomb scattering.

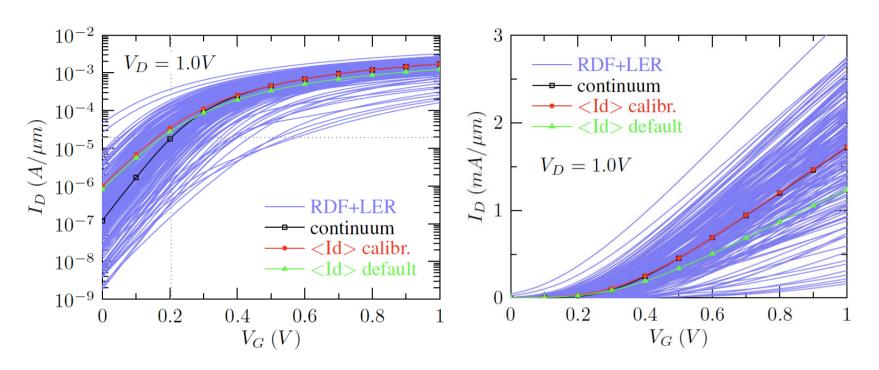

#### The calibration dilemma

- The shape of the continuous simulation and the average 'atomistic'

I-V curves are different.

- □ The calibration of continuous TCAD simulations to measurements which are equivalent to average atomistic simulation results in compensations through the mobility models..

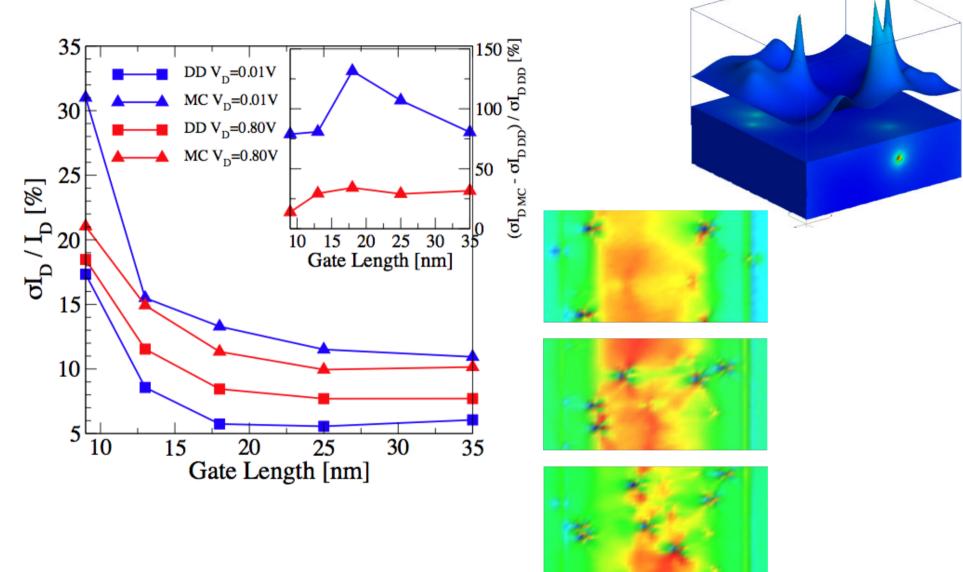

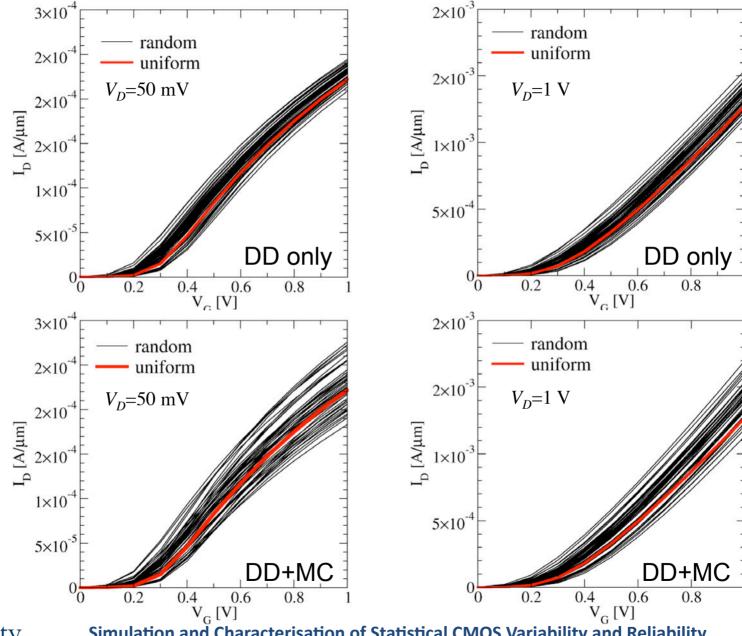

Transport (scattering) related variability

#### The impact of the transport related variability

35 nm MOSFET

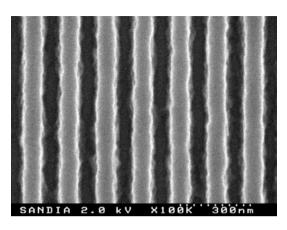

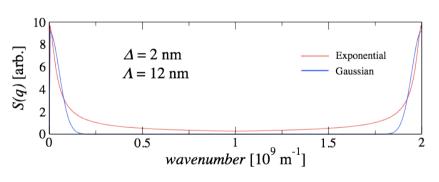

### LER is notoriously difficult to reduce

Sandia Labs - EUV

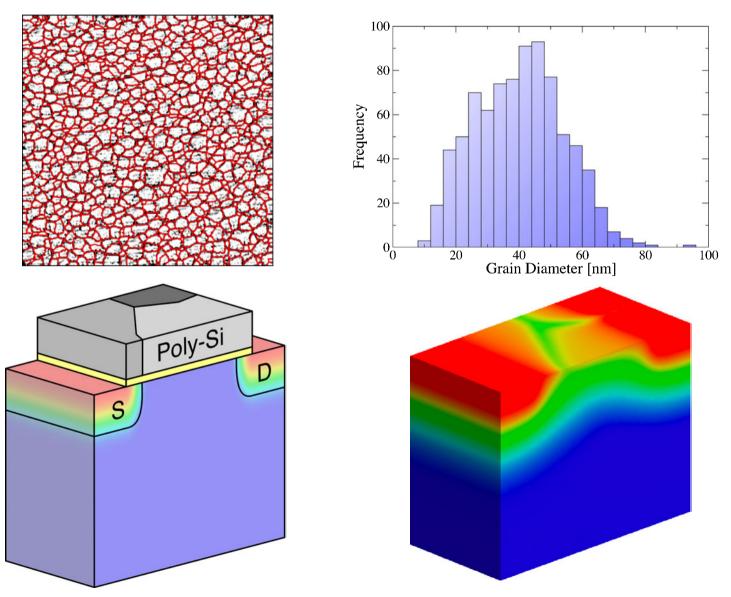

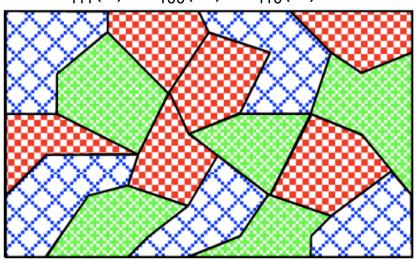

### **Poly-Silicon Grains**

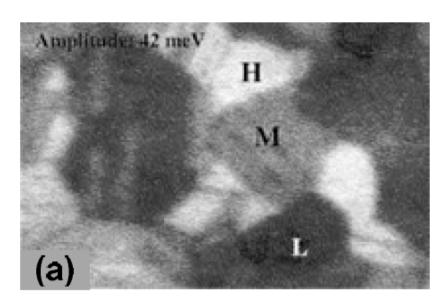

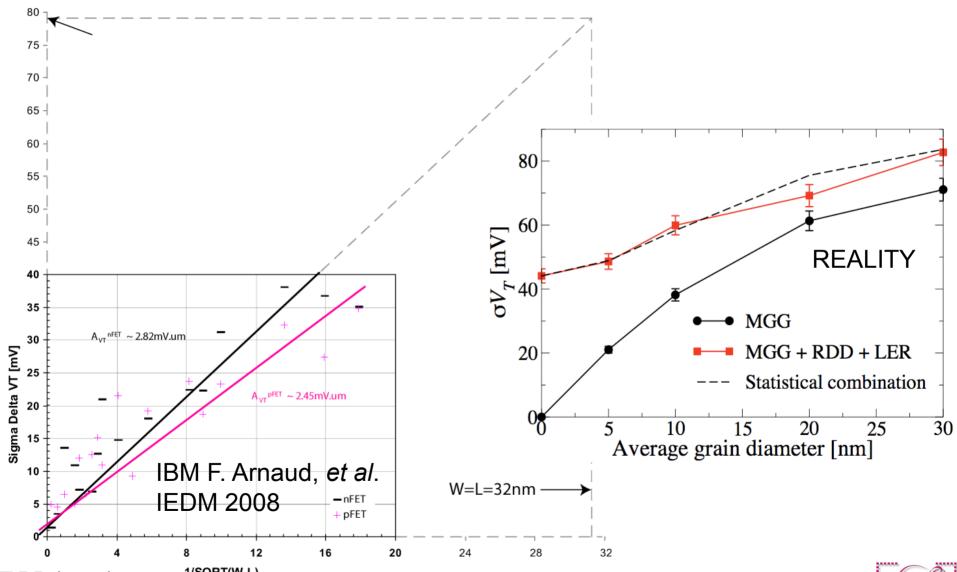

# Metal gate granularity (MGG)

$$\Phi_{111}(L)>\Phi_{100}(M)>\Phi_{110}(H)$$

#### Statistical reliability: electrostatics

Simulation and Characterisation of Statistical CMOS Variability and Reliability SISPAD Workshop, Bologna 9/9/2010

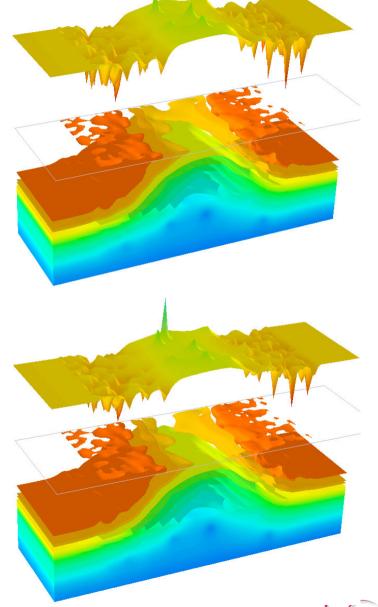

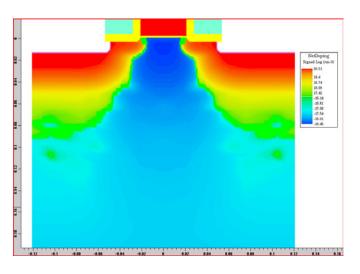

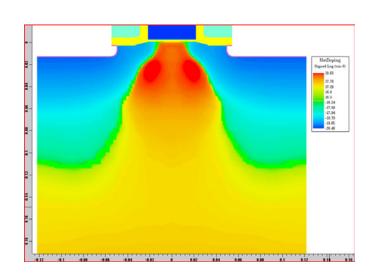

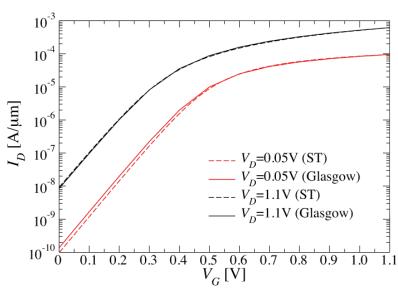

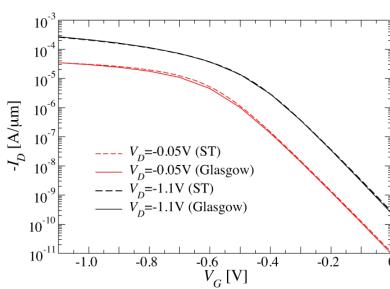

# Example: 45nm Device Structure and Calibration

# Good agreement with measurements

|              | <i>n</i> -channel         | MOSFET                   | <i>p</i> -channel MOSFET  |                          |  |

|--------------|---------------------------|--------------------------|---------------------------|--------------------------|--|

|              | $\sigma V_T$ [mV]         | $\sigma V_T$ [mV]        | $\sigma V_T$ [mV]         | $\sigma V_T$ [mV]        |  |

|              | $(V_{DS}=0.05 \text{ V})$ | $(V_{DS}=1.1 \text{ V})$ | $(V_{DS}=0.05 \text{ V})$ | (V <sub>DS</sub> =1.1 V) |  |

| RDD          | 50                        | 52                       | 51                        | 54                       |  |

| LER          | 20                        | 33                       | 13                        | 22                       |  |

| PSG          | 30                        | 26                       | -                         | -                        |  |

| Combined     | 62                        | 69                       | 53                        | 59                       |  |

| Experimental | 62                        | 67                       | 54                        | 57                       |  |

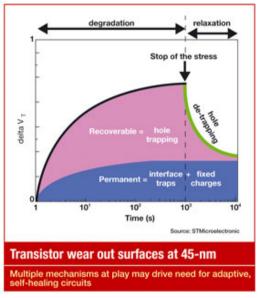

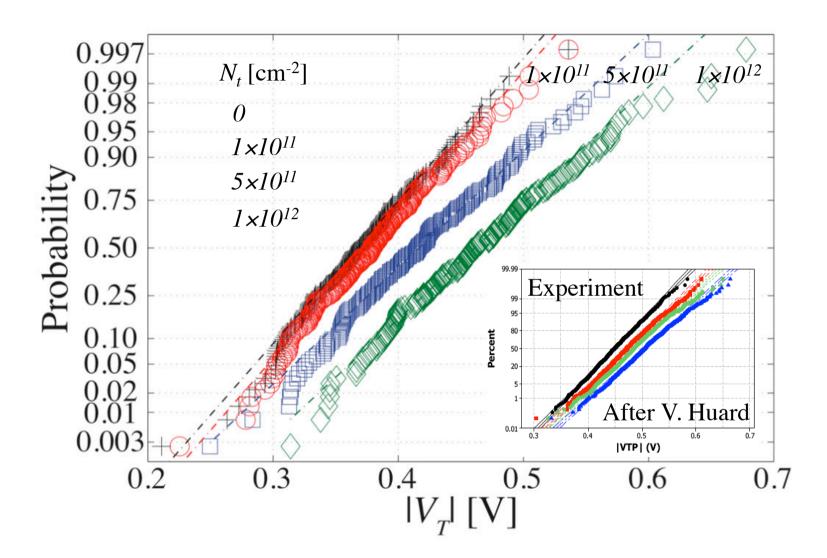

### Trapped charges (NBTI)

# Trapped charges (NBTI)

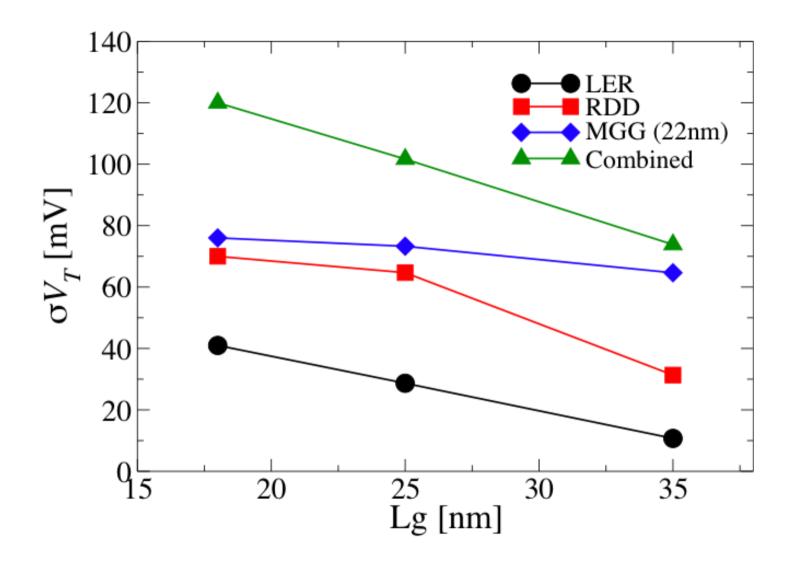

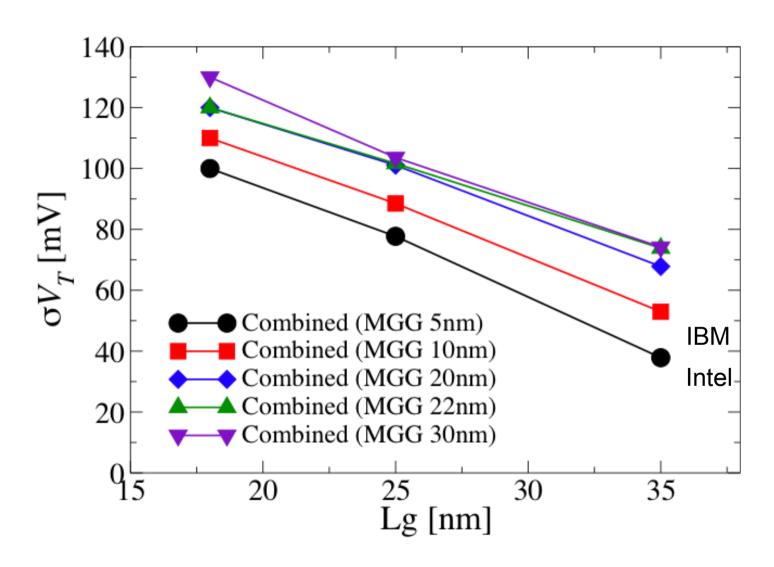

#### 32nm Metal Gate Granularity

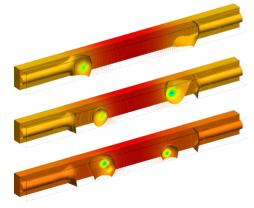

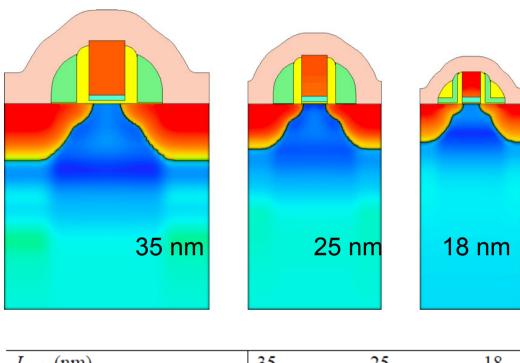

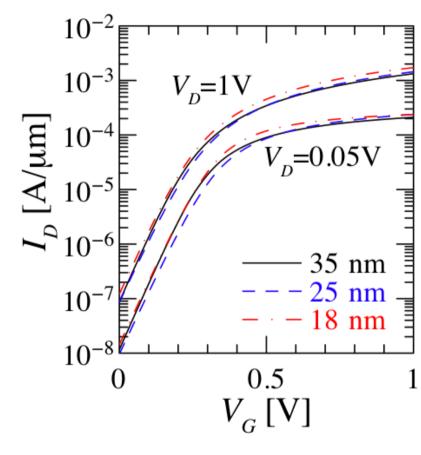

## Updated scaling – high-k/metal gate

| $L_{gate}$ (nm)                 | 35  | 25  | 18  |

|---------------------------------|-----|-----|-----|

| EOT (nm)                        | 1.0 | 0.9 | 0.7 |

| Stress liner thickness (nm)     | 30  | 22  | 15  |

| Lateral length (nm)             | 200 | 130 | 100 |

| $V_{dd}\left(\mathbf{V}\right)$ | 1.0 | 1.0 | 1.0 |

## Variability in high-k/metal gate MOSFETs

## Variability in high-k/metal gate MOSFETs

#### SOI and DG variability

32 nm FD SOI

22 nm DG

|                 | $32$ nm $\sigma$ | $V_T(mV)$      | 22nm σ          | $V_T(mV)$       |

|-----------------|------------------|----------------|-----------------|-----------------|

|                 | $V_{ds}$ (50mV)  | $V_{ds}(1.0V)$ | $V_{ds}$ (50mV) | $V_{ds}$ (1.0V) |

| RDD             | 5.3              | 6.1            | 6.4             | 8.1             |

| LER             | 3.3              | 8.6            | 5.8             | 13              |

| Trap (1e11)     | 11               | 11             | 5.1             | 4.8             |

| Trap (5e11)     | 24               | 25             | 13              | 12              |

| Trap (1e12)     | 36               | 37             | 18              | 17              |

| Combined (1e11) | 13               | 15             | 10              | 16              |

| Combined (5e11) | 25               | 27             | 16              | 19              |

| Combined (1e12) | 37               | 38             | 20              | 23              |

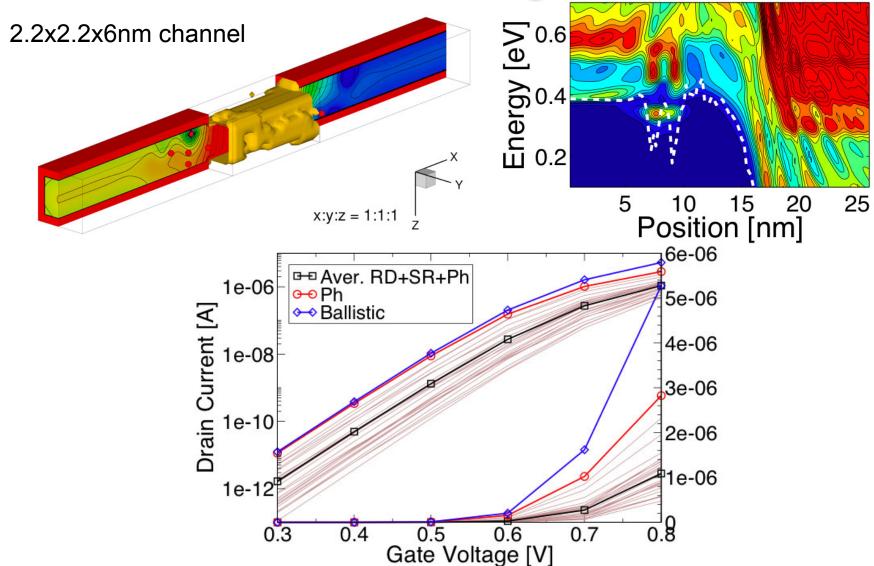

# 3D NEGF simulator with variability and scattering

#### Conclusions

- There is a large amount of research being done in Europe on the study of variability and ways to deal with it in circuits and systems

- Underpinning this work are TCAD simulations which quantify the variability at a device level

- The major sources of statistical variability have been highlighted and some of the issues involved in including them in TCAD modelling have been discussed.